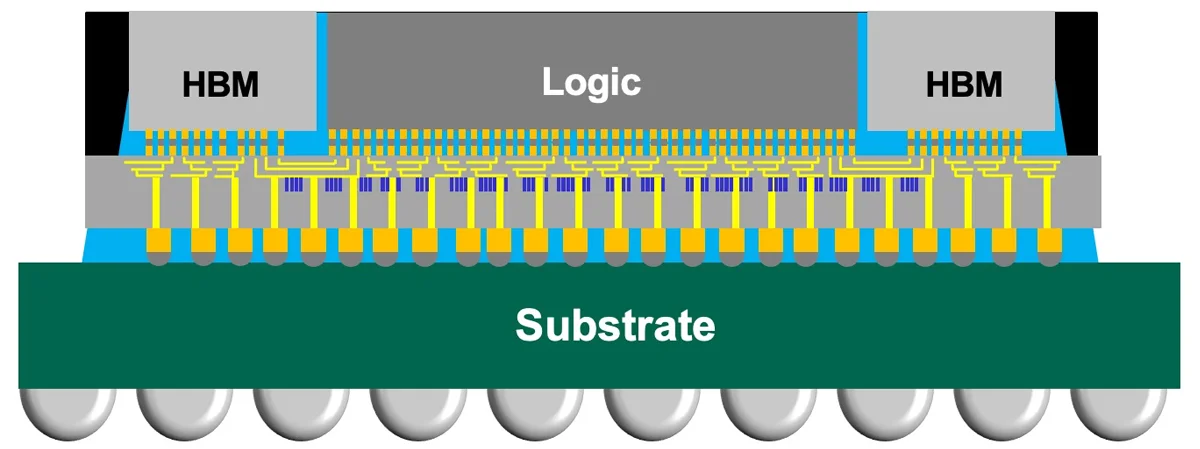

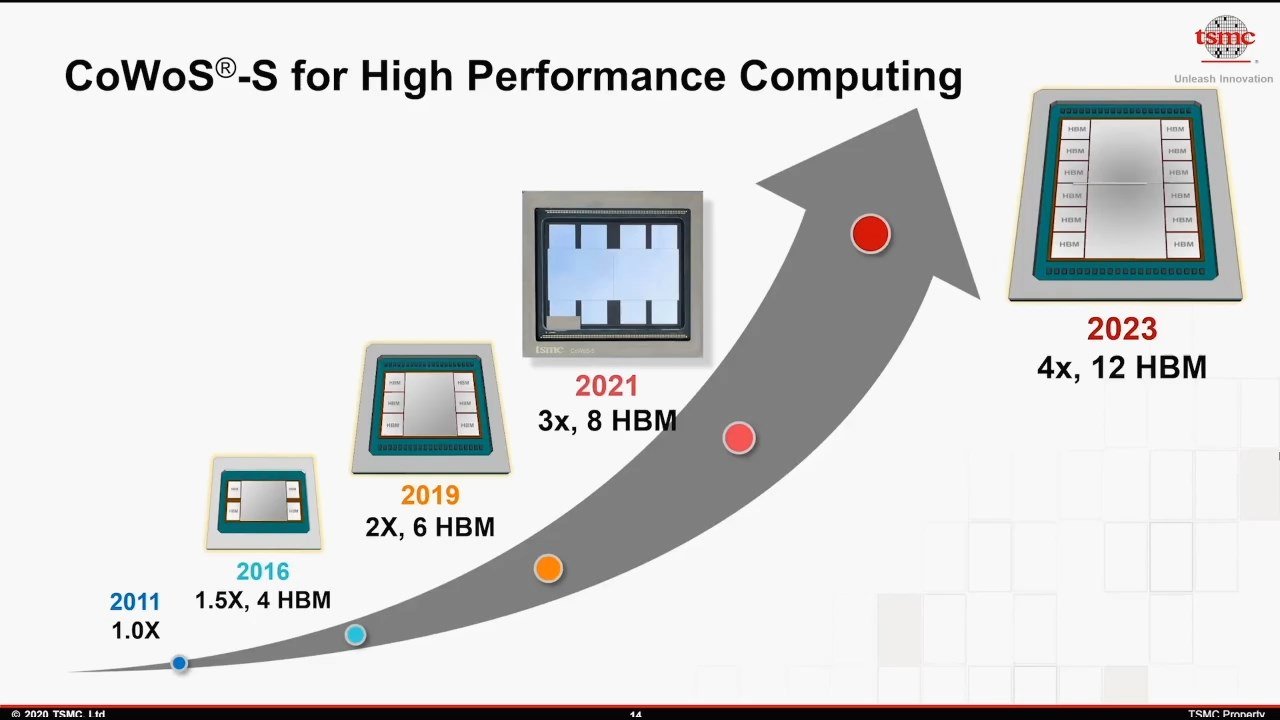

CoWoS có 3 phiên bản với CoWoS-S là bản đầu tiên. Chữ S là viết tắt của silicon interposer, trong đó các chip SoC lẫn HBM sẽ “alo” với nhau qua tấm đệm này. Sau lần xuất hiện đầu tiên trên AMD Fury-X, CoWoS-S gần như trở thành tiêu chuẩn cho các hãng khác “học theo”. Song CoWoS-S có nhược điểm là giới hạn reticle dùng đế sản xuất ra tấm silicon. Ở lần ra mắt đầu tiên với Fury-X, diện tích tấm silicon chỉ gấp 1.5 lần giới hạn reticle EUV (có nghĩa chỉ nhét được 1 die SoC + 4 die HBM). Tới 2019, TSMC mới cải thiện được lên 2 lần (1 die SoC + 6 die HBM). Phiên bản 2021 là gấp 3 lần (lúc này mới gắn được 2 die SoC) và 2023 thì được 4 lần (vẫn chỉ được 2 die SoC kèm thêm các die HBM).

Silicon interposer có tốc độ cao nhưng chi phí sản xuất cao và sản lượng hạn chế

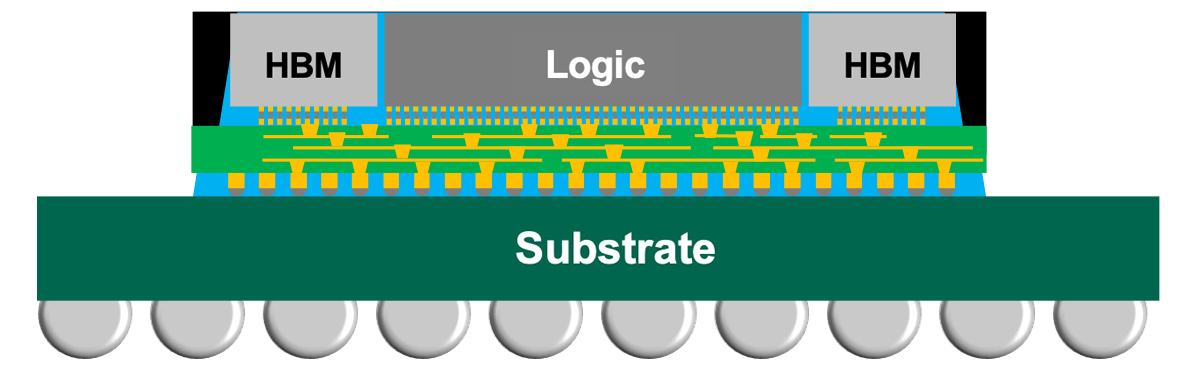

Và dù có thể làm ra tấm silicon bự hơn, không có nghĩa là sản lượng của chúng cao hơn. Một quy luật của lithography là kích thước die càng lớn thì hiệu suất càng giảm. CoWoS-S cũng không thoát được chuyện này. Do đó TSMC phải tìm tới giải pháp khác nếu như không muốn “đâm đầu vô tường” trước cả định luật Moore. Cái khó ló cái khôn, TSMC tìm được lối thoát ngay từ chính mình – RDL và LSI.

CoWoS-R và CoWoS-L thực chất là sự kết hợp giữa InFO và CoWoS. Trong đó thay vì dùng tấm silicon đắt đỏ thì TSMC dùng RDL có chi phí chế tạo thấp hơn. Ngoài ra, do đặc tính vật liệu hữu cơ nên RDL có hệ số giãn nở vì nhiệt ổn hơn Si, giúp giảm thiểu tình trạng giãn nở không đồng bộ giữa các die chip và mạch liên kết cũng như tấm nền và PCB ở dưới. Đối với các ứng dụng gần tới băng thông cực cao, cầu LSI sẽ vào cuộc. Vì thế CoWoS-R và CoWoS-L là giải pháp thay thế nếu khách hàng muốn làm những con chip siêu bự như trường hợp GB200 Blackwell của NVIDIA. Thực tế gần đây có thông tin NVIDIA đã bỏ dùng CoWoS-S để chuyển hoàn toàn sang CoWoS-L cho các chip Blackwell sau này.