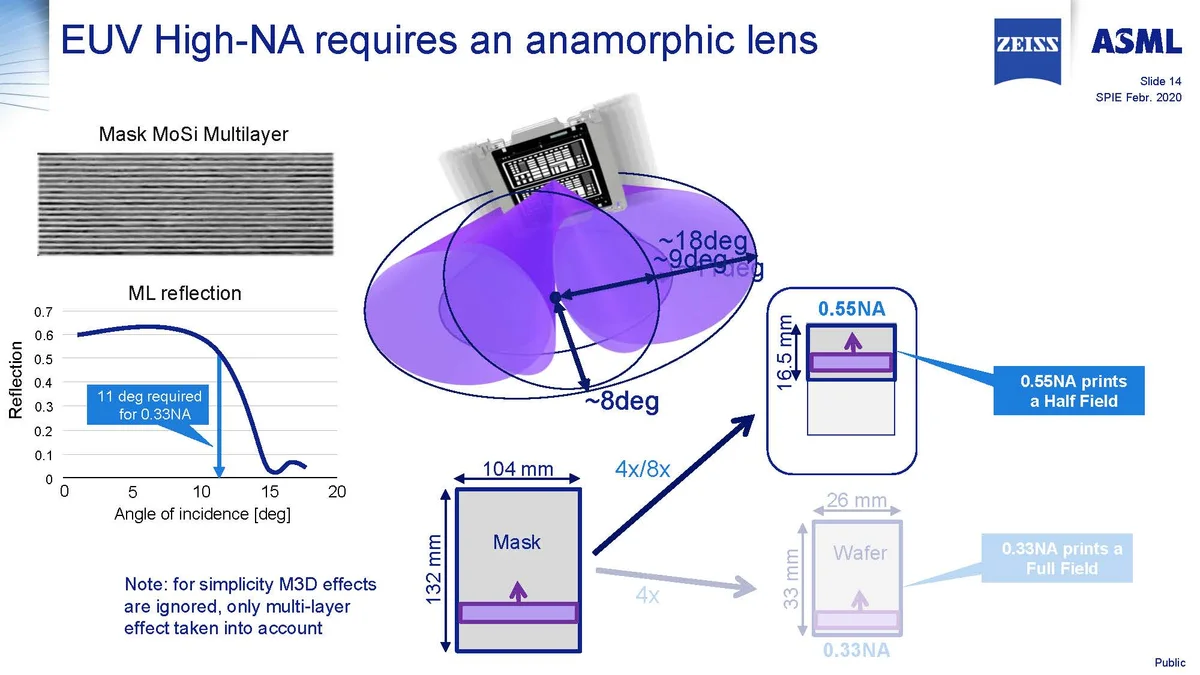

Tất nhiên vào 1965, thế giới cũng chưa có khái niệm về thiết kế MCM (multi-die module) hay chiplet. Nên không thể bảo logic của Moore bao hàm cả chiplet. Nhìn chung, một mạch IC với mình là một die chip duy nhất. Và thiết kế monolithic đang dần tới hồi kết như đã nêu ở trên. Để đạt hệ số NA cao (giúp vẽ mạch bán dẫn chi tiết hơn) thì giới hạn recticle/photomask càng nhỏ lại. Mà diện tích die hẹp lại thì số transistor có thể “nhồi nhét” vào dĩ nhiên là cũng giảm. Tính tới hiện tại, một die monolithic dựa trên node TSMC N3 có thể đạt tối đa khoảng 170 tỷ transistor (197 triệu/mm2 * 858 mm2), nhưng đó là trên lý thuyết, thực tế thấp hơn rất nhiều (vì còn phải chia phần cho SRAM). Nên có thể nói cứ đi “con đường” monolithic thì sớm muộn bạn cũng “đâm đầu vô tường”.

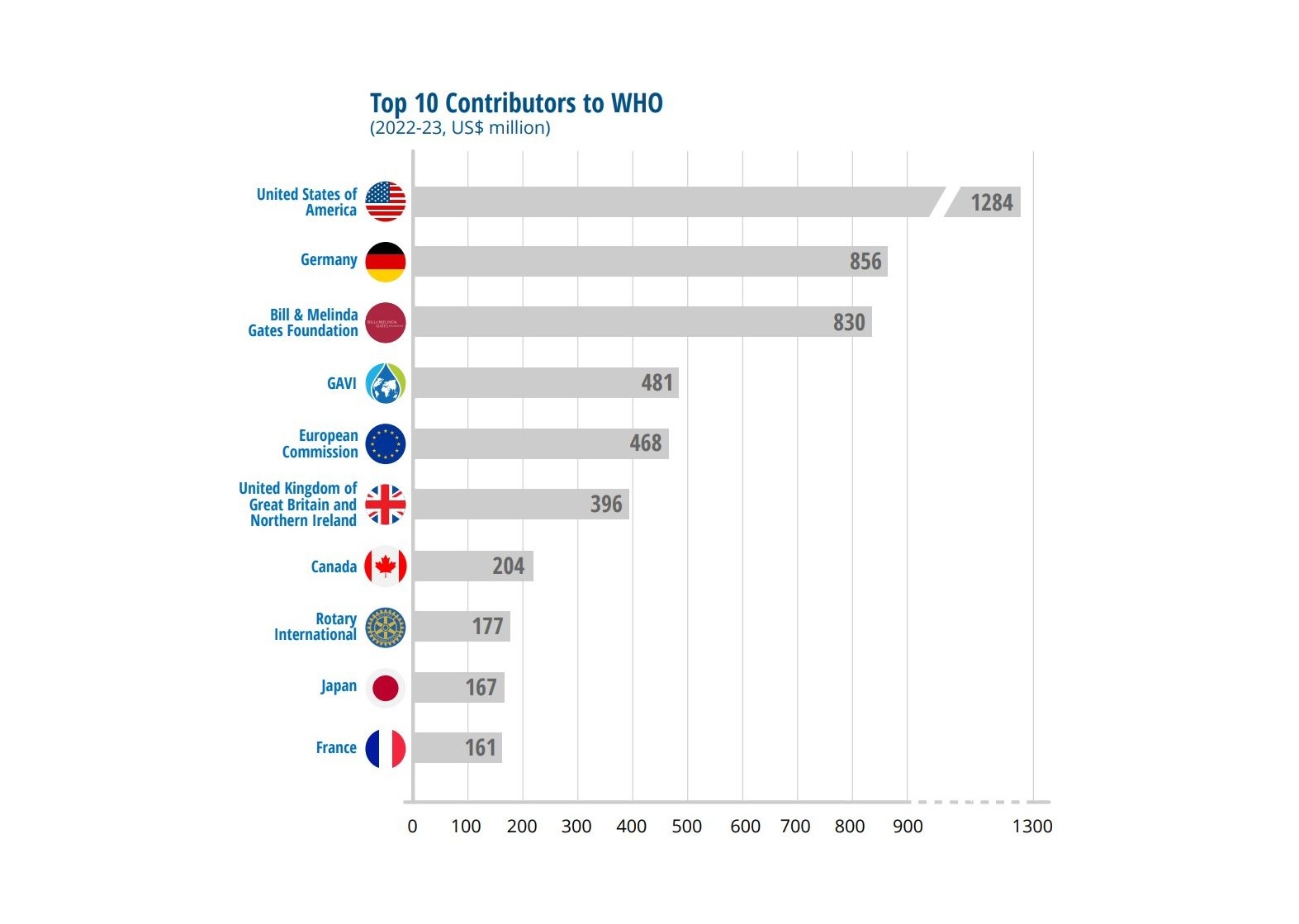

Do giới hạn quang học, High-NA EUV sẽ có diện tích die tối đa chỉ bằng 1/2 0.33 NA EUV

Nên vấn đề rõ mười mươi là bạn không thể làm monolithic mãi được (tạm bỏ qua các ứng dụng không cần “đua bơi” transistor như hạ tầng mạng, điện tử gia dụng, chip quân sự…). MCM hoặc chiplet là lối thoát duy nhất cho các hãng chip hiệu năng cao.

À vâng, chiplet, thứ này đã tồn tại cả chục năm qua rồi. Có gì mới ở đây? Bạn đang thắc mắc.

Cái mới ở đây chính là khác biệt trong cách sản xuất một con chip Ryzen/EPYC vs. MI300. Nếu chỉ áp dụng những kỹ thuật làm ra con Ryzen đầu tiên thì AMD/TSMC không thể nào chế tạo được MI300. Để có thể làm ra được MI300, TSMC phải vận dụng gần như mọi “skill” mà công ty này có được tính tới hiện tại. Nói hơi quá thì đây là “quest” khó nhất mà AMD từng đề ra cho công ty Đài Loan. Thậm chí có thể nói cả Samsung Foundry lẫn Intel Foundry cũng không làm được tính tới thời điểm này. Đây cũng là lý do tại sao mình chọn MI300 thay vì Ponte Vecchio hay GB200 – mình không nói rằng 2 con chip sau không phức tạp, nhưng độ phức tạp của MI300 còn nhiều hơn thế.